Ridurre i consumi energetici e accelerare l’elaborazione di grandi quantità di dati è l’obiettivo del nuovo chip sviluppato da un gruppo di ricercatori del Dipartimento di Elettronica, Informazione e Bioingegneria (DEIB) del Politecnico di Milano.

Il progetto, guidato dal docente Daniele Ielmini, è stato presentato nello studio pubblicato sulla prestigiosa rivista Nature Electronics, con primo autore il ricercatore Piergiulio Mannocci.

Il progetto "Animate"

Il lavoro nasce all’interno del progetto ANIMATE (ANalogue In-Memory computing with Advanced device Technology) che si era aggiudicato un ERC Advanced Grant nel 2022.

Questo studio partiva dalla ricerca preliminare di Daniele Ielmini sul CL-IMC (Closed-Loop In-Memory Computing), ovvero il calcolo in-memoria ad anello chiuso, e sulle opportunità che offriva: ridotti tempi per la risoluzione di calcoli e fino a 5.000 volte meno energia rispetto ai computer digitali.

Obiettivo del progetto ANIMATE era proprio lo sviluppo della tecnologia per il dispositivo, circuiti, architetture di sistema e l’insieme di applicazioni atti a validare il CL-IMC.

Come funziona il chip per calcolo in-memoria ad anello chiuso

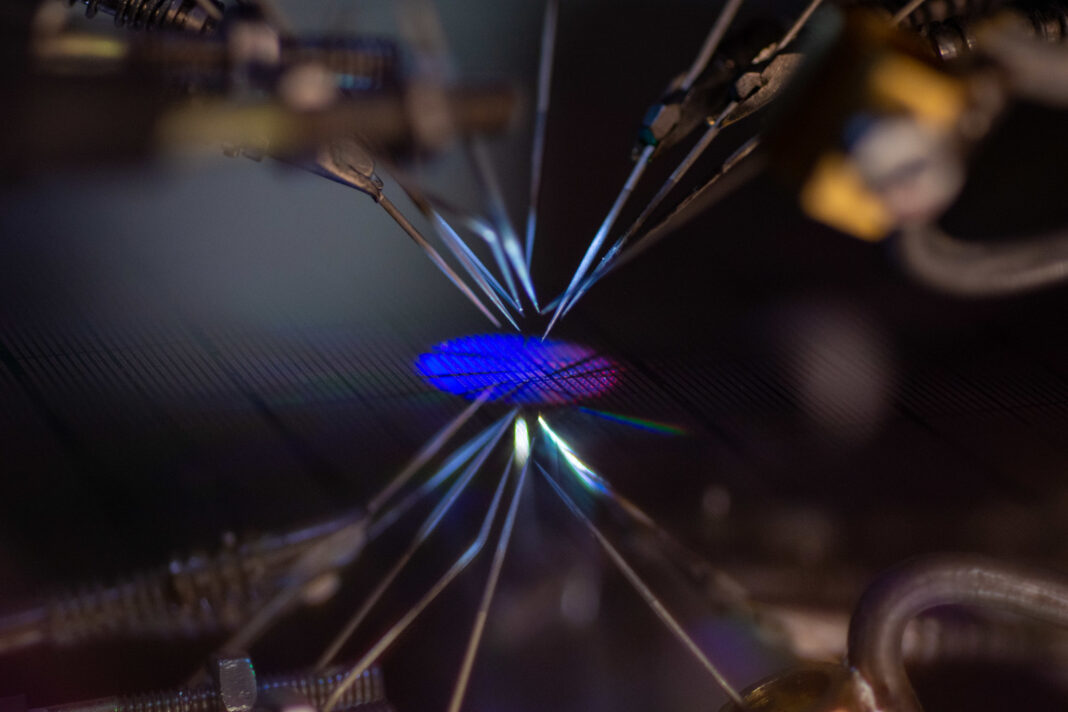

Il chip elaborato si avvale, appunto, del calcolo in-memoria che si propone di superare un limite dei computer: la necessità di spostare continuamente i dati tra memoria e processore.

Eliminando questo “traffico” interno, i sistemi diventano più veloci ed energeticamente efficienti.

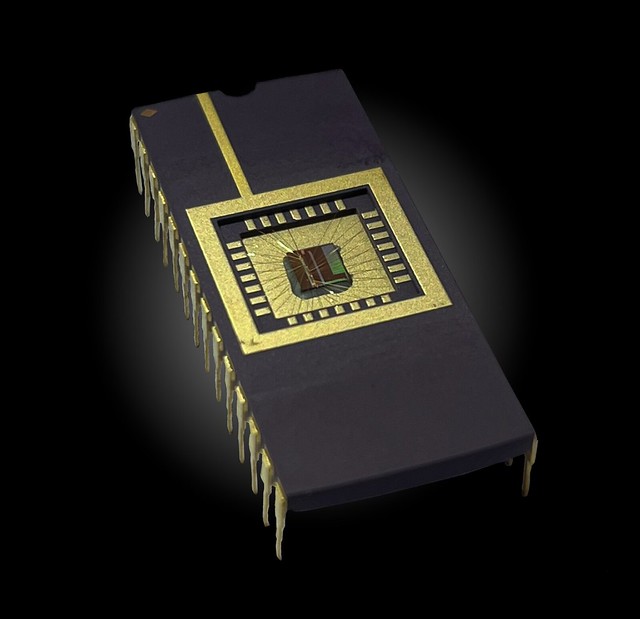

Nello studio appena pubblicato, il team del DEIB presenta un acceleratore analogico completamente integrato per la soluzione di sistemi di equazioni lineari e non lineari, realizzato in tecnologia CMOS (Complementary Metal-Oxide-Semiconductor), un processo standard per la fabbricazione di circuiti integrati su silicio.

Calcoli complessi, senza spostare i dati verso un processore esterno

Il dispositivo utilizza due array 64×64 di memorie resistive programmabili. Ricordiamo che un array è una sorta di “griglia ordinata” composta da elementi identici disposti in righe e colonne, simile a un foglio a quadretti, dove ogni incrocio tra una riga e una colonna rappresenta una cella di memoria.

Le celle utilizzate sono basate su tecnologie SRAM (Static Random-Access Memory), un tipo di memoria veloce e stabile, qui combinata con resistori integrati che consentono di programmare diversi livelli di resistenza. L’architettura è completata da uno schema di elaborazione analogica che sfrutta componenti integrati nel chip, come amplificatori operazionali e convertitori analogico-digitali.

L’insieme permette al sistema di affrontare calcoli complessi direttamente all’interno della struttura di memoria, evitando di spostare i dati verso un processore esterno. In questo modo si riducono i tempi di calcolo in modo significativo.

Nei test, il chip ha raggiunto un’accuratezza simile a quella dei sistemi digitali tradizionali, ma con minori consumi energetici, ridotta latenza di calcolo e un ingombro sul silicio più contenuto.

La portata rivoluzionaria del calcolo analogico in-memoria

"Il chip integrato dimostra la fattibilità su scala industriale di un concetto rivoluzionario come il calcolo analogico in-memoria", ha spiegato Daniele Ielmini, docente del DEIB e alla guida del gruppo di ricerca. "Siamo già al lavoro per trasferire questa innovazione in applicazioni nel mondo reale per ridurre i costi energetici del calcolo, soprattutto nell’ambito dell’intelligenza artificiale".

Il lavoro si basa su una collaborazione internazionale anche con la Peking University, e un team eterogeneo che ha coinvolto professori, ricercatori, dottorandi e studenti.

Le opportunità per l'industria del chip per calcolo in-memoria

Lo studio rappresenta un passo avanti importante verso dispositivi più compatti, veloci e sostenibili, aprendo nuove prospettive per la ricerca e per l’industria.

Il calcolo in-memoria è una soluzione ideale, infatti, in contesti che richiedono alte prestazioni ed elevata efficienza energetica come l’intelligenza artificiale, l’elaborazione di grandi quantità di dati e i sistemi di comunicazione wireless di nuova generazione.

Le applicazioni spaziano dalla robotica ai data center, dai sistemi di navigazione fino alle reti di telecomunicazione avanzate, come il 5G e le future tecnologie 6G.